Independent Watchdog timer of STM32

Table of contents

What is a watchdog timer?

A watchdog timer is a function that detects when a program has runaway or frozen, terminates the program, and resets it. It is called a watchdog timer because of its role in watching for program abnormalities.

It is very common for an application program to suddenly freeze under some influence on a PC. This is because the program has somehow accidentally entered an infinite loop and cannot accept any operations from the outside, in other words, it has become frozen. In the case of a PC, there is no other way but to forcibly turn the power back on and restart it, but this is not the case with embedded devices.

Therefore, the watchdog timer function is used to terminate the program and automatically apply a forced reset when a problem occurs. The watchdog timer function does not detect an abnormality, but rather, when a timeout is reached without clearing the counter value, which would normally clear the counter value, the program is deemed abnormal and the program is terminated and a forced reset is applied.

This function may not be necessary for hobbyist electronics work, but it is necessary for industrial and medical equipment that operates 24 hours a day.

Independent Watchdog timer

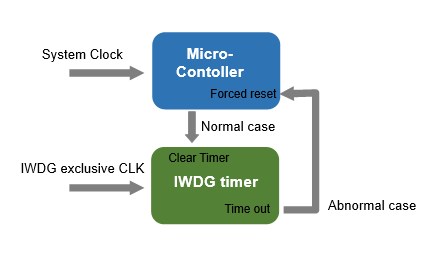

The STM32 microcontroller uses the LSI internal clock for the watchdog timer clock. Since the system clock is supplied from an external HSE or internal HIS, it is an independent clock and can detect problems without being affected even if trouble should occur with the system clock. For this reason, it is called an independent watchdog.

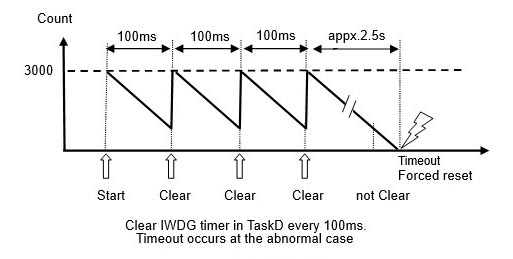

The timer is a down counter and starts from the set value immediately after the count value is cleared and counts down. If the count value is not cleared halfway and reaches an underflow, the microcontroller is forced to reset. Therefore, it is necessary to clear the counter value before the underflow, or timeout, is reached.

The following is an explanation of the actual program settings.

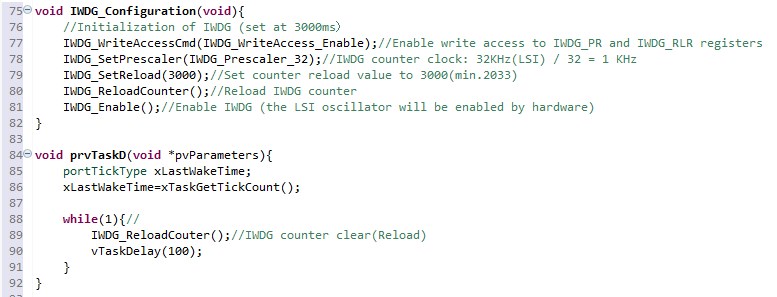

Immediately after program startup, the stand-alone watchdog is disabled from writing to registers by default, so IWDG_WriteAccessCmd() is used to be enable write access to the registers. The argument is IWDG_WriteAccess_Enable to allow access and IWDG_WriteAccess_Disable to disable access.

Execution Example of function: IWDG_WriteAccessCmd(IWDG_WriteAccess_Enable);

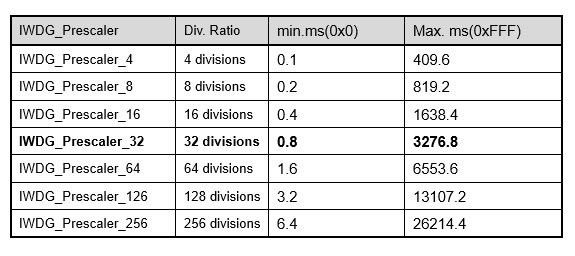

Next, the clock division ratio of the watchdog timer is set with IWDG_SetPrescaler(). There are seven arguments to the function, ranging from 4 to 256. The table below summarizes the times that can be set by the division ratio when the LSI is 40 kHz.

Since the LSI is an internal clock, there is some variation in frequency, but if you want to set the watchdog timer at approximately 2500 ms, specify a frequency divider ratio of 32.

Execution Example of function: IWDG_SetPrescaler(IWDG_Prescaler_32);

The counts are set by IWDG_SetReload(). The argument of the function must be a number between 0x0 and 0xFFF (4095) and must be 3000.

Execution Example of function: IWDG_SetReload(3000);

The counter value of the watchdog timer is cleared with IWDG_ReloadCounter(). The counter is forced to reset at the set counter value (approximately 2500 ms at 3000), so the counter is cleared within this period, for example, within TaskD, which is performed at 100 ms intervals.

Counter clearing should be performed by the task with the lowest priority, considering the function of the watchdog. During normal operation, TaskD with the lowest priority can clear the counter since it is executed almost every 100ms, but if some abnormality occurs and the watchdog freezes, TaskD is not executed and the counter cannot be cleared, and the watchdog timer will reach a timeout, resulting in a forced reset. The following table shows the number of times the program has been run.